# Design and Performance of Clock-Recovery GaAs ICs for High-Speed Optical Communication Systems

Yuhki Imai, *Member, IEEE*, Eiichi Sano, *Member, IEEE*, Makoto Nakamura, *Member, IEEE*, Noboru Ishihara, *Member, IEEE*, Hiroyuki Kikuchi, *Member, IEEE*, and Takashi Ono

**Abstract**—Design and performance of clock-recovery GaAs ICs are presented. Four kinds of ICs were developed: a limiting amplifier, a tuning amplifier, a rectifier, and a differentiator. The cascaded limiting amplifier together with a tuning amplifier achieved a 58-dB gain and a 10-degree phase deviation with 20-dB input dynamic range at 10 GHz. A clock-recovery circuit successfully extracts a low-jitter 10-GHz clock signal of 1-dBm constant power from 10-Gb/s NRZ pseudorandom bit streams using a pulse pattern generator.

## I. INTRODUCTION

RECENTLY, optical communication systems operating at 10 Gb/s data rates are attracting considerable interest for high-capacity communication systems [1]. A key component to realize such systems is a high-speed clock recovery circuit. Monolithic integration is also required to achieve compact and low-cost systems that offer fail-safe reliability. Several high-speed clock-recovery ICs have been developed using GaAs MESFETs and heterostructure devices [2]–[4]. GaAs ICs are clearly the most realistic candidates to realize the systems considering the maturity of this material system and device technology. GaAs IC technologies have already been applied to 10-Gb/s data-recovery circuits and they have demonstrated excellent performance. [5]–[7]. A key design issue for clock-recovery circuits is how to reduce phase deviation over a wide dynamic range in a limiting amplifier because this has a great impact on recovered-lock phase deviation and jitter.

This paper describes design techniques and performance of GaAs clock-recovery ICs for high-speed optical communication systems. Four kinds of IC are covered: a limiting amplifier, a tuning amplifier, a rectifier, and a differentiator. A noteworthy feature of the limiting-amplifier design is that it suppresses spurious harmonic signals to reduce phase deviation. The other ICs feature a tuning amplifier with a voltage-controlled tuning frequency, a Gilbert-cell-based rectifier, and a differentiator with an on-chip  $\lambda/4$  coplanar-waveguide short stub, respectively.

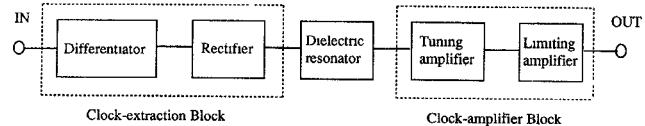

Fig. 1. Block diagram of clock-recovery circuit.

## II. CIRCUIT DESIGN

A block diagram of the clock-recovery circuit is shown in Fig. 1. It consists of a differentiator IC, a rectifier IC, a dielectric resonator, a tuning amplifier IC, and limiting amplifier ICs. The differentiator and rectifier extract a clock signal from a data signal. A high-Q dielectric resonator is used for a timing tank. A tuning amplifier acts as an active band-pass filter to suppress the jitter caused by the high-order mode of the dielectric resonator [4]. Limiting amplifier ICs were cascaded to obtain a high gain of 60 dB. Circuit simulation was performed using an FET model with an  $f_T$  of 40 GHz and an  $f_{max}$  of 70 GHz.

### 1. Limiting Amplifier

Because a clock's amplitude from a dielectric resonator is strongly modulated by a data pattern, a limiting amplifier is required to maintain low phase deviation over a wide input dynamic range to provide an aligned clock for a decision circuit. In previous studies [8], [9], emphasis was placed on minimizing the signal phase delay as a way to reduce the phase deviation. In these studies, the circuit was simplified to avoid additional phase delay or the pole frequency was increased to reduce phase delay at the operating frequency. In this paper we will concentrate on the effects spurious harmonics have on phase deviation.

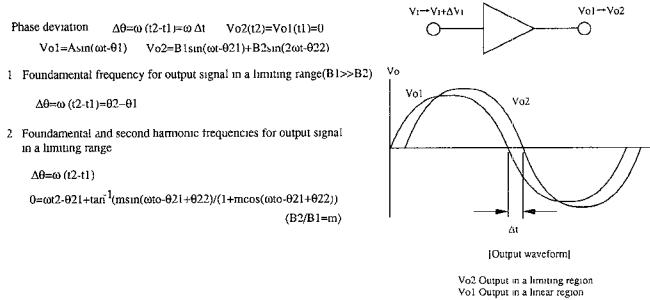

A limiting amplifier operates under highly non-linear conditions when it limits the output power. High-order harmonics are generated in the limiting operation and they also have phase deviation. The harmonics thus affect the phase deviation of the total output waveform. A schematic illustrating the effect when a second harmonic is dominant is shown in Fig. 2. Phase deviation is defined as the variation in input-to-output signal phase shift to the input power variation. Since the phase deviation is very small in any linear region, we can redefine phase deviation in Fig. 2 for convenience to refer specifically to the phase shift from an output signal in a linear region to that in a limiting region. Here,  $\theta_{21}$  and  $\theta_{22}$  are the phase deviations of output fundamental and second-harmonic

Manuscript received April 27, 1992; revised September 21, 1992.

Y. Imai, E. Sano, M. Nakamura and N. Ishihara are with NTT LSI Laboratories, 3-1 Morinosato Wakamiya, Atsugi 243-01, Japan.

H. Kikuchi is with NTT Electronics Technology, 3-1 Morinosato Wakamiya, Atsugi 243-01, Japan.

T. Ono is with NTT Transmission Systems Laboratories, 1-2365 Take, Yokosuka 243-03, Japan.

IEEE Log Number 9207426.

Fig. 2. Effect of second harmonic on phase deviation.

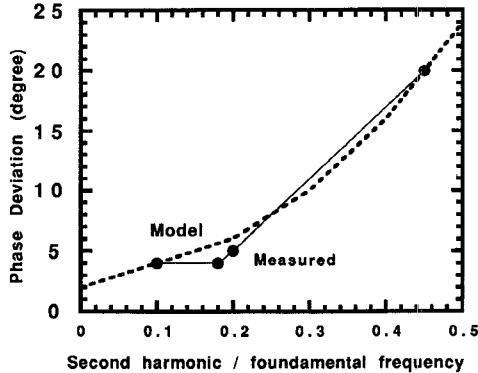

Fig. 3. Phase deviation versus ratio of fundamental frequency to second harmonic. Solid line: Experimental results. Dashed line: Calculated results.

frequencies. They are affected by the powers of the input signal and generated second harmonics, respectively, due to the nonlinear bias dependence of the transistor capacitances. When a second harmonic is not negligible in a limiting region, the phase deviation of the total waveform is related to that of the second harmonic ( $\theta_{22}$ ) as illustrated in the simple analytical formula shown in Fig. 2. Phase deviation increases as  $\theta_{22}$  or/and the ratio of the fundamental to the second harmonic frequency ( $m$ ) increase.

Experimental results respecting the second harmonic effect on the phase deviation are shown in Fig. 3. The phase deviation is plotted a function of the amplitude ratio of the output fundamental frequency to the output second harmonic. For this experiment, the suppression of the second harmonic was varied using different-frequency-band amplifier ICs with the same 10-GHz gain, structure and transistors combined with an external filter. Frequency and dynamic range of the input signal were 10 GHz and 15 dB. Phase deviation was measured using a sampling oscilloscope with 40-GHz sampling head. It was found that the phase deviation fell off sharply as the second harmonic decreased. Calculated results using the analytical formula with  $\theta_{21}$  and  $\theta_{22}$  as fitting parameters are also shown in Fig. 3. We assume that  $\theta_{22}$  varies inversely with the second-harmonic amplitude. While it is very difficult to specify the cause of  $\theta_{21}$  and  $\theta_{22}$  in quantitative forms, it is nevertheless apparent that the simple analytical model explains the experimental results quite well.

As the above results make clear, suppression of the second harmonic is very effective for reducing the phase deviation

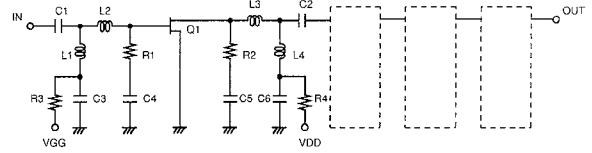

Fig. 4. Schematic of limiting amplifier.

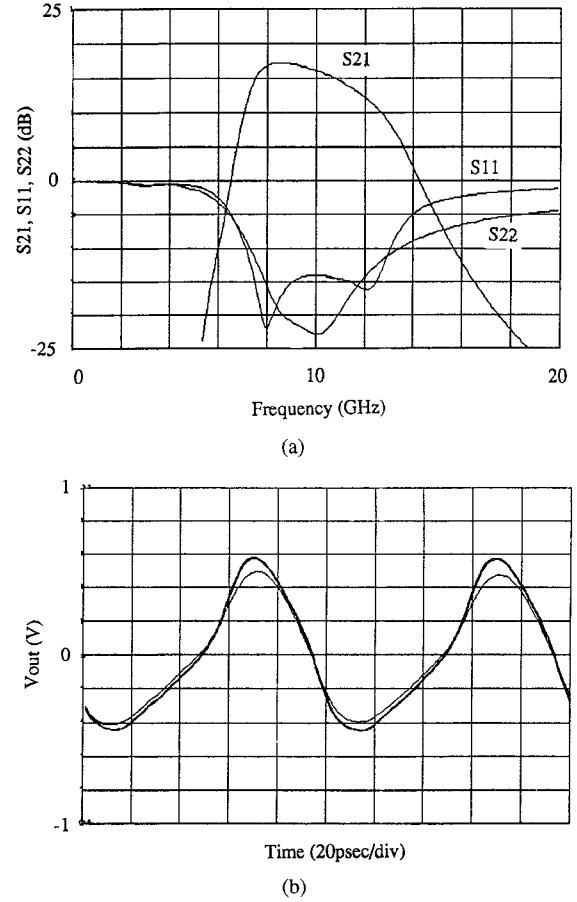

Fig. 5. Simulated results for limiting amplifier. (a) frequency dependencies of  $S_{21}$ ,  $S_{11}$ , and  $S_{22}$ . (b) Output waveforms for input powers of  $-10$ ,  $0$ ,  $5$ ,  $10$  dBm.

of a limiting amplifier. In actual circuits, a differential configuration [2] or a narrow-band configuration which suppresses second harmonic frequency is suited to suppress the second harmonic because of its simplicity. In the present design, a narrow-band configuration was chosen because it is also capable of easily deriving a high gain at microwave frequencies thanks to inherent high-f<sub>max</sub> performance of GaAs MESFETs. Note that this is a completely different approach than tried in previous studies because almost all limiting amplifiers for optical communication systems have employed wideband configurations [2], [3], [8], [9]. A schematic circuit of the limiting amplifier is shown in Fig. 4. It has a 4-stage construction with input, output and interstage impedance-matching networks. The gate width of FET is  $100 \mu\text{m}$ . The multi-stage construction was used to reduce the peak gate-to-drain voltage applied to each FET during a limiting operation. Simulated results are presented

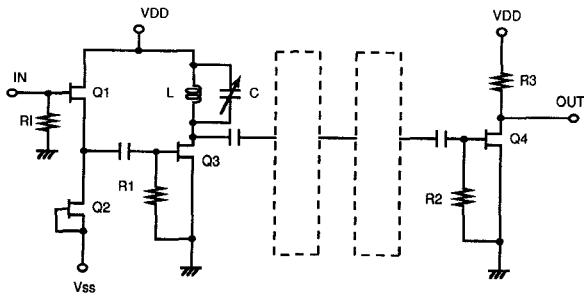

Fig. 6. Schematic of tuning amplifier.

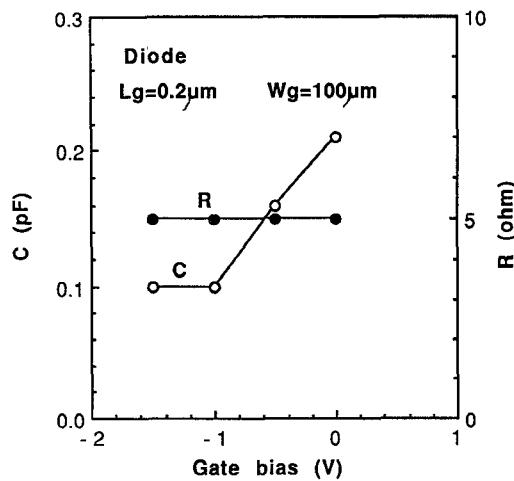

Fig. 7. Bias dependencies of capacitance and resistance for diode.

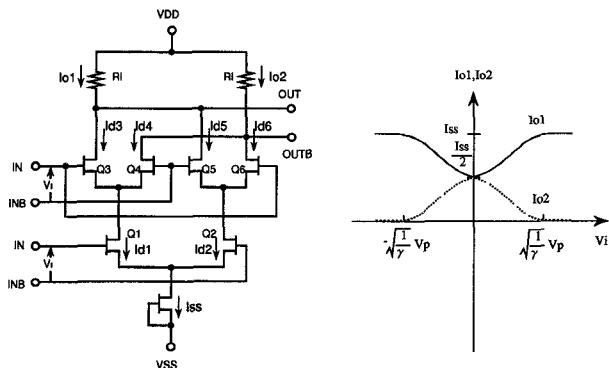

Fig. 8. Schematic for Gilbert cell and transfer characteristic.

in Fig. 5. They were simulated using a modified MESFET model based on hyperbolic tangent  $I_{ds}$ - $V_{ds}$  relation [8]. Bias dependencies of equivalent-circuit parameters were extracted by fitting the measured  $S$  parameters. Simulated results include extrinsic effects of bonding-wire inductances. Four output waveforms for input powers of  $-10, 0, 5, 10$  dBm are traced in Fig. 5. The amplifier was designed to yield a gain of more than 15 dB with  $S_{11}$  and  $S_{22}$  less than  $-14$  dB at 10 GHz. Simulated output signals reveal very small phase deviation up to an input power of 10 dBm.

TABLE I

TRANSFER CHARACTERISTIC OF GILBERT CELL

|                                |                                                                                                                                           |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| $I_{ds}$                       | $\frac{I_{ds}}{2} \left( 1 + \left( \frac{V_i}{V_p} \right)^2 \left( 2\gamma - \gamma^2 \left( \frac{V_i}{V_p} \right)^2 \right) \right)$ |

| $G_c$                          | $2K \frac{V_i}{V_p} \left( 2 - \left( \frac{V_i}{V_p} \right)^2 \right)$                                                                  |

| $I_{di}$<br>( $i = 1, 2$ )     | $K (V_{gs} - V_p)^2 = I_{ds} \left( 1 - \frac{V_{gs}}{V_p} \right)$                                                                       |

| $I_{di}$<br>( $i = 3 \sim 6$ ) | $K' (V_{gs} - V_p)^2 = I_{ds} \left( 1 - \frac{V_{gs}}{V_p} \right)$                                                                      |

| $\gamma$                       | $\frac{I_{ds}}{I_{ds}} = \frac{I_{ds}}{I_{ds}}$                                                                                           |

| $G_c$                          | $\frac{\partial I_{ds}}{\partial V_i}$                                                                                                    |

Fig. 9. Schematic of rectifier.

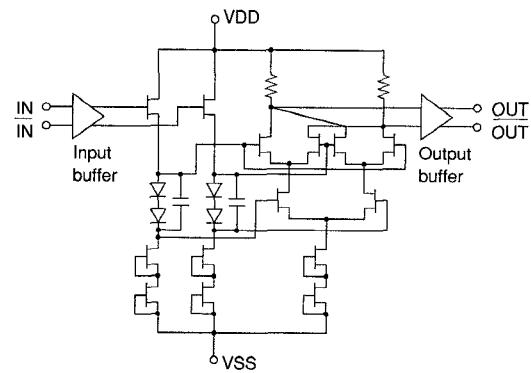

Fig. 10. Schematic of differentiator.

## 2. Tuning Amplifier

An LC parallel-resonance circuit was employed for a tuning amplifier. A schematic circuit is shown in Fig. 6. It consists of a common-source FET with an LC resonance circuit on the drain side. A small gate width of  $25 \mu\text{m}$  was used to increase the FET output resistance parallel to the LC resonance circuit. Three tuning stages were cascaded to increase the gain and  $Q$  factor at the tuning frequency. For the inductance, a monolithic spiral inductor of  $1 \text{ nH}$  with  $2\Omega$  series resistance was employed. The tuning frequency was voltage-controlled using the variable capacitance of a diode. Bias dependencies of the capacitance and series resistance are shown in Fig. 7. The diode employs the same structure as that of a MESFET with ion-implanted channel and  $n^+$  layers. Impedance matchings

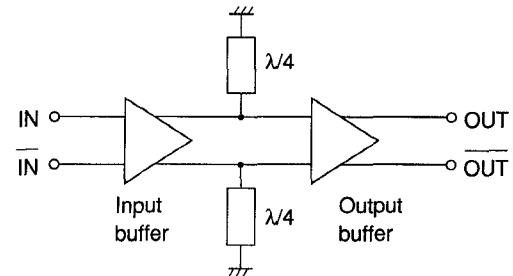

Fig. 11. Microphotographs of ICs. (a) Limiting amplifier. (b) Tuning amplifier. (c) Rectifier. (d) Differentiator.

were obtained in a wide frequency band with source-follower and common-source FETs as buffers. The gain was designed to be 10 dB at a tuning frequency of 10 GHz with gain reduction of about 20 dB at frequencies 2-GHz removed from the tuning frequency. A tuning frequency was changed by about 2 GHz using the controlled bias.

### 3. Rectifier

A Gilbert cell [10] operates as either doubler or full wave rectifier when the signals with the same frequency or shape are applied at two differential input ports. A schematic Gilbert cell circuit and transfer characteristics are shown in Fig. 8. The analytical expressions of the transfer characteristics are also shown in Table I. The transfer characteristic was derived using a cubic I-V formula for MESFETs with a threshold voltage  $V_p$ . A Gilbert cell operates as a doubler with small spurious output signals when the input signal  $Vi$  is small enough compared with  $V_p$  to neglect high-order terms of  $Vi/V_p$ . For relatively large input signals, it operates as a full wave rectifier because of the symmetric transfer characteristic. Since spurious output signals were rejected by the next-stage dielectric resonator used for the clock-recovery circuit, the Gilbert-cell was de-

signed to operate as a full wave rectifier for this work. Fig. 9 shows a schematic of the entire circuit. A differential amplifier was used as an active balun for an input buffer. Input signals were split in-phase and applied at Gilbert-cell input ports by level-shifters. Input and output buffers also provided good impedance matchings over a wide frequency range.

### 4. Differentiator

A schematic differentiator circuit is shown in Fig. 10. A  $\lambda/4$  short stub was employed to different signals. Compared with an  $RC$  differentiator, a  $\lambda/4$  differentiator is less affected by fabrication parameter variations. The short stub was monolithically integrated using a compact meandering coplanar waveguide.

## III. FABRICATION

ICs were fabricated using advanced self-aligned implantation for  $n^+$  layer technology (ASAINT) [11]. The gate length and threshold voltage were 0.2  $\mu\text{m}$ , and  $-0.8$  V. The  $f_t$  and  $f_{max}$  of the MESFETs were 40 GHz and 70 GHz, respectively. Microphotographs of the ICs are shown in Fig. 11. Chip sizes were  $1.5 \times 2.5$  mm for the limiting amplifier,  $2 \times 1.5$  mm for

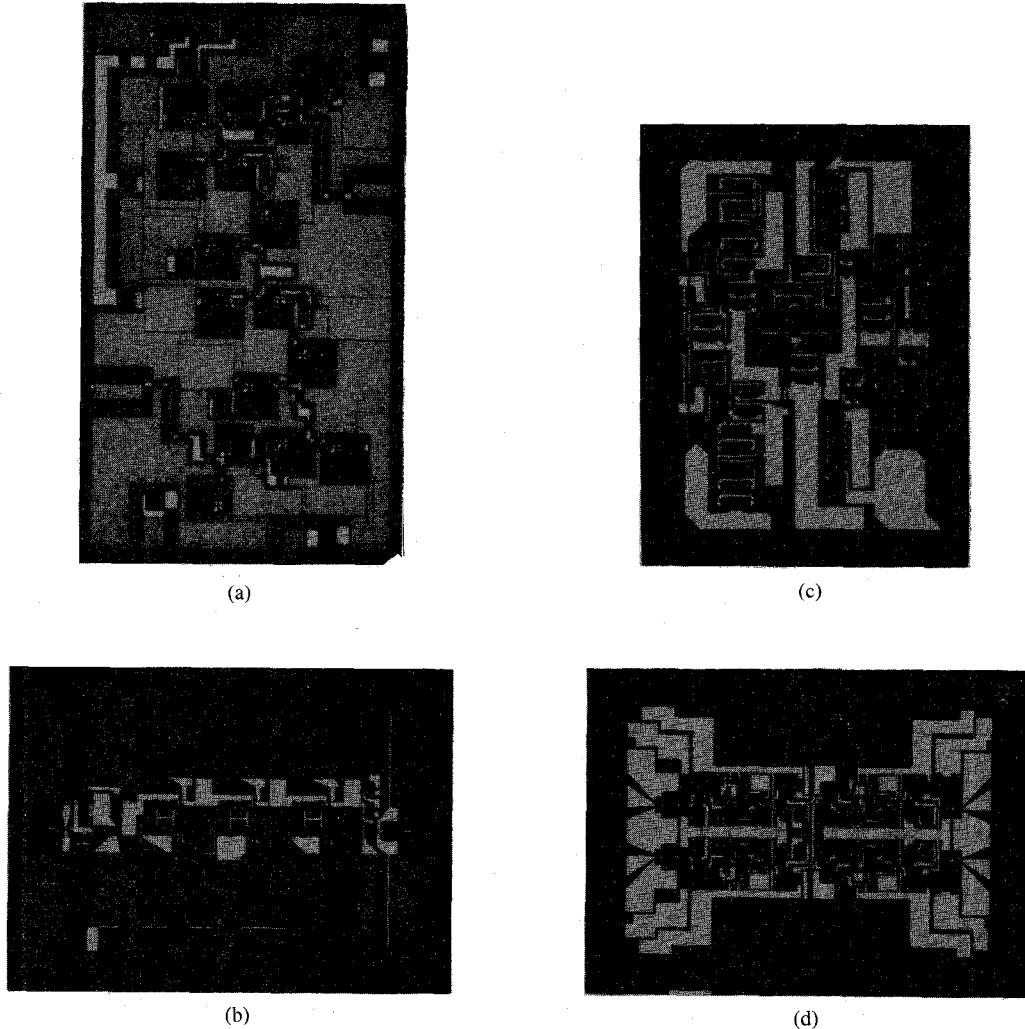

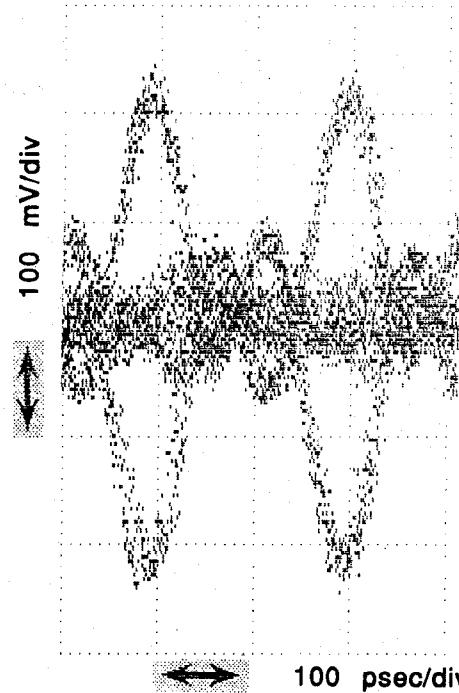

Fig. 12. Waveform characteristics of clock-extraction block for 10-Gb/s NRZ PRBS signal. (a) Output waveform of differentiator. (b) Output waveform of clock-extraction block. (c) Monitored waveform for inverting input data.

the tuning amplifier,  $1.5 \times 2$  mm for the rectifier, and  $2 \times 1.5$  mm for the differentiator. After all ICs were subjected to on-wafer testing, they were encased in metal-based packages [6]. The package has a cavity size of  $6 \times 3.5$  mm with coplanar-waveguide signal lines. The isolation was more than 50 dB at 10 GHz.

#### IV. PERFORMANCE

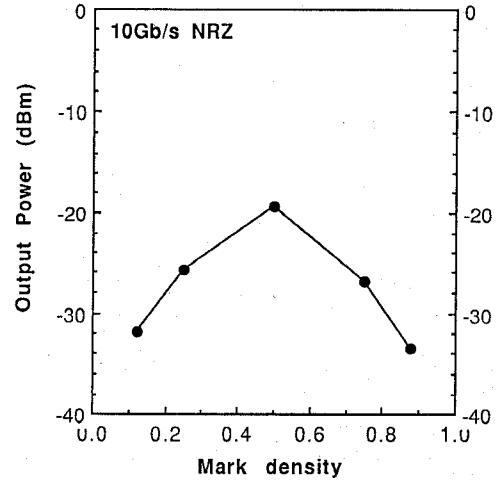

##### 1. Clock-Extraction Block

Packaged differentiator and rectifier ICs were cascaded to construct a clock-extraction block (Fig. 1). OUT and OUT nodes of the differentiator were dc-connected to IN and IN nodes of the rectifier. Input data and a reference voltage were applied to IN and IN ports of the rectifier, respectively. Supply voltages were 5 V and  $-3$  V with a total power consumption of about 1.2 W. Fig. 12 shows output waveforms of the differentiator and clock-extraction block for input data of 10 Gb/s NRZ  $2^{23} - 1$  pseudorandom bit streams (PRBS) from a pattern generator. High and low levels of input data were 0 V and  $-0.9$  V. Monitored input inverting data are also shown in Fig. 12. The ICs operated very well up to the speeds of 10 Gb/s. The output waveform of the differentiator showed a slight ripple. This is because of the  $50 \Omega$  termination of the  $\lambda/4$  short stub was not perfect, giving rise to a reflection. A differentiator output for 5-Gb/s NRZ input signal is also shown in Fig. 13 to illustrate the function of a  $\lambda/4$  short stub. A pulse train with about 50-psec pulse width and 200-psec period was generated by the differentiator. The pulse width corresponds to  $\lambda/2$  at 10 GHz. The mark-density dependencies of the extracted clock-signal power are shown in Fig. 14. Clock signal powers of  $-20$  to  $-34$  dBm were extracted over a mark-density range from  $1/8$  to  $7/8$ .

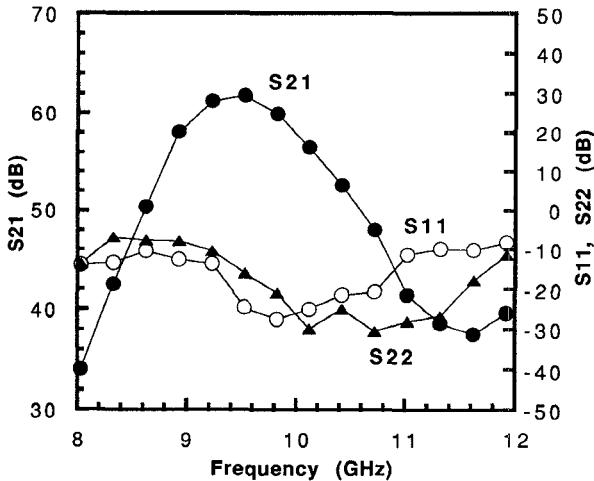

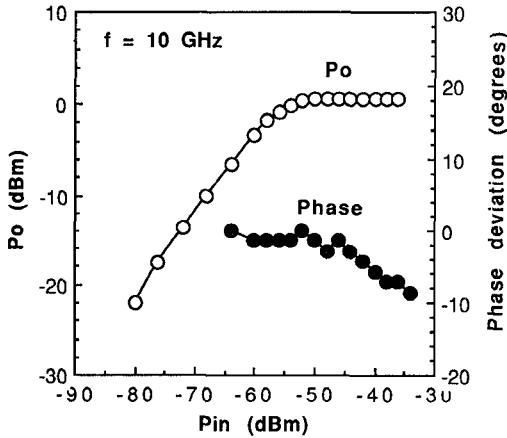

##### 2. Clock-Amplifier Block

One packaged tuning amplifier and four packaged limiting amplifier ICs were cascaded to produce clock-amplifier block (Fig. 1). Supply voltages were 1 V and  $-3$  V with a total power consumption of 130 mW. Frequency dependencies of

Fig. 13. Output waveform of differentiator for 5-Gb/s NRZ PRBS signal.

Fig. 14. Mark-density dependencies of extracted clock-signal power.

$S21$ ,  $S11$  and  $S22$  for the amplifier block are shown in Fig. 15. The amplifier had a high gain of 58 dB with  $S11$  and  $S22$  of less than  $-20$  dB at 10 GHz. Good bandpass performance was obtained with a gain reduction of more than 15 dB at 8 and 12 GHz. The gain reduction was well enough to suppress the increase in jitter due to high-order modes of the dielectric resonator.  $S21$  peaked at 9.5 GHz because the tuning frequency of the tuning amplifier shifted beyond the variable-frequency range and couldn't be adjusted by the control bias. It is because the tuning frequency was affected by the extrinsic inductances of IC patterns and bonding wires more than expected in the design. The input-power dependencies of output power and phase deviation are shown in Fig. 16. The amplifier achieved a small phase deviation of less than 10 degrees with a saturated power of 1 dBm in the input dynamic range from  $-55$  dBm to  $-35$  dBm.

Fig. 15. Frequency dependencies of  $S_{21}$ ,  $S_{11}$  and  $S_{22}$  for clock-amplifier block.

Fig. 16. Output power and phase deviation versus input power for clock-amplifier block.

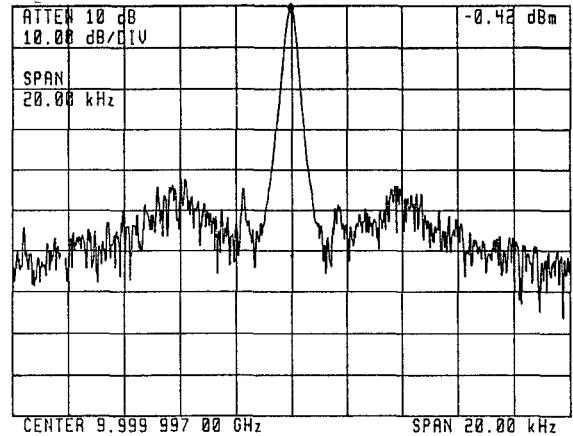

### 3. Clock-Recovery Circuit

The clock-recovery circuit shown in Fig. 1 was tested using the clock-extraction and amplifier blocks. The dielectric resonator had about 6-db loss at 10 GHz with a Q factor of about 1000. Attenuators were inserted into the circuit to adjust the power level. Fig. 17 shows the frequency spectrum of an output signal for input data of 10 Gb/s NRZ  $2^{23}-1$  PRBS from a pattern generator. RMS jitter of the recovered clock signal was 1.4 degrees at a mark density of 1/2 and was maintained within 2.5 degrees in the mark-density range centering on 1/2 from 1/8 to 7/8.

### V. CONCLUSION

Design techniques and performance of GaAs clock-recovery ICs for application to high-speed optical communication systems were described. The key feature of the limiting-amplifier design that we highlight in this paper is that spurious harmonic signals are suppressed to reduce phase deviation. Noteworthy features of the other ICs were a tuning amplifier with a voltage-controlled tuning frequency, a Gilbert-cell-based rectifier, and a differentiator with an on-chip  $\lambda/4$  coplanar-waveguide short

Fig. 17. Frequency spectrum of recovered clock signal for clock-recovery circuit.

stub, respectively. Combining these techniques, a 10-Gb/s GaAs clock-recovery circuit was successfully developed. Considering their overall performance—high speed, high gain, and small size—these devices should have a considerable impact on high-speed optical communication systems.

### ACKNOWLEDGMENT

The authors wish to thank Y. Akazawa for his valuable circuit design insights and continuous encouragement. They also thank Y. Yamane and K. Hagimoto for their valuable discussions and the colleagues of NTT Electronics Technology Corporation for fabricating of the ICs. The authors also express appreciation to N. Leda, K. Nakagawa and H. Ishio for their continuous encouragement.

### REFERENCES

- [1] K. Hagimoto, Y. Miyagawa, Y. Miyamoto, M. Ohhashi, M. Ohhata, K. Aida, and K. Nakagawa, "A 10 Gb/s long-span fiber transmission experiment employing optical amplification techniques and monolithic IC technology," in *Tech. Dig. IOOC*, Kobe, Japan, 1989, post-deadline paper 20PDPA-6.

- [2] M. Nakamura, Y. Imai, E. Sano, Y. Yamauchi, and O. Nakajima, "15-GHz AlGaAs/GaAs HBT limiting amplifier with low phase deviation," *IEEE GaAs IC Symp. Tech. Dig.*, 1991, pp. .

- [3] J. Akagi, Y. Kuriyama, K. Morizuka, M. Asaka, K. Tsuda, M. Obara, H. Yamakawa, and H. Ibe, "AlGaAs/GaAs HBT receiver ICs for a 10 Gbps optical communication system," *IEEE GaAs IC Symp. Tech. Dig.*, 1990, pp. 45-48.

- [4] T. Ono, K. Hagimoto, M. Nakamura, N. Ishihara, and H. Kikuchi, "Reduction of RMS jitter and phase deviation in 10 Gbit/s timing recovery circuit using monolithic ICs," *Electron Lett.*, vol. 28, pp. 403-404, Feb. 1992.

- [5] Y. Imai, E. Sano, and K. Asai, "Design and Performance of wideband GaAs MMIC's for high-speed optical communication systems," *IEEE Trans. Microwave Theory Tech.*, vol. 40, pp. 185-190, Feb. 1991.

- [6] N. Ishihara, E. Sano, Y. Imai, H. Kikuchi, and Y. Yamane, "A design technique for a high-gain, 10-GHz class-bandwidth GaAs MESFET amplifier IC module," *IEEE J. Solid-State Circuits*, vol. 27, pp. 554-562, Feb. 1991.

- [7] M. Togashi, M. Ohata, K. Murata, H. Kindo, M. Ino, M. Suzuki, and Y. Yamane, "10-Gb/s GaAs MESFET ICs for ultra high-speed transmission system," *IEEE GaAs IC Symp. Tech. Dig.*, 1990, pp. 49-52.

- [8] T. Wakimoto, Y. Akasawa, and K. Kawarada, "4-GHz band GaAs monolithic limiting amplifier," *IEEE J. Solid-State Circuits*, vol. SC-21, pp. 1103-1108, Dec. 1986.

- [9] N. Ishihara, H. Kikuchi, and M. Ohara, "1 GHz band high gain Si monolithic limiting amplifiers using parallel feedback technique," *IEICE Trans.*, vol. E 70, pp. 383-384, Apr. 1987.

- [10] B. Gilbert, "A high-performance monolithic multiplier using active feedback," *IEEE J. Solid-State Circuits*, vol. SC-9, pp. 364-373, Dec. 1974.

- [11] Y. Yamane, M. Ohhata, H. Kikuchi, K. Asai, and Y. Imai, "A 0.2  $\mu$ m GaAs MESFET technology for 10 Gbit/s digital and analog ICs," in *1991 IEEE MTT-S Int. Microwave Symp. Dig.*, vol. Q-1, pp. 513-516.

**Yuhki Imai** (M'92) was born in Tokyo, Japan, on March 15, 1955. He received the B.S., M.E., and Dr.Eng. degrees in applied physics from Waseda University in 1977, 1979, and 1981, respectively.

He joined the NTT Electrical Communication Laboratories, Musashino, Tokyo, Japan, in 1979, where he has been engaged in the development of GaAs MESFETs and ICs. In 1989 he joined the NTT LSI Laboratories, where he is currently engaged in the development of GaAs ICs for lightwave communications.

Dr. Imai is a member of the Institute of Electronics, Information and Communication Engineers of Japan.

**Eiichi Sano** (M'84) was born in Shizuoka, Japan, on December 4, 1952. He received the B.S. and M.S. degrees from the University of Tokyo, Tokyo, Japan, in 1975, and 1977, respectively.

In 1977, he joined the Electrical Communications Laboratories, NTT, Tokyo, Japan. He has been engaged in the research on MOS device physics, performance limits of mixed analog/digital MOS ULSI's, ultrafast photoconductive switches and electro-optic sampling technology for measuring high-speed devices. His current research interests

include high-speed electronic and optoelectronic devices for optical communication.

Mr. Sano is a member of the Institute of Electronics, Information and Communication Engineers of Japan.

**Makoto Nakamura** (M'92) was born in Gifu, Japan, on July 9, 1964. He received the B.S. and M.S. degrees in electronic engineering from Nagoya University, Nagoya, Japan, in 1987 and 1989, respectively.

In 1989, he joined LSI Laboratories, Nippon Telegraph and Telephone Corporation (NTT), Kanagawa, Japan. He has been engaged in research and design of clock recovery circuits and broad-band amplifier for optical communication systems.

Mr. Nakamura is a member of the Institute of Electronics and Communication Engineers of Japan and the Institute of Electrical Engineers of Japan.

**Noboru Ishihara** (M'89) was born in Gunma, Japan, on April 27, 1958. He received his B.S. degree in electrical engineering from Gunma University, Gunma, Japan, in 1981.

In 1981, he joined the Electrical Communication Laboratory, NTT, Tokyo, Japan, where he has been engaged in research and development of high-speed analog IC's for communication use. His recent work is in the area of low-power and high-speed analog IC's.

Mr. Ishihara is a member of the Institute of Electronics, Information and Communication Engineers of Japan.

**Hiroyuki Kikuchi** (M'89) was born in Tokyo, Japan, on April 28, 1948. He received the B.S. and M.S. degrees in electronic engineering from Keio University, Kanagawa, Japan, in 1972 and 1974, respectively.

In 1974 he joined NTT Electrical Communication Laboratory, Tokyo, Japan. He initially did research and development work on CMOS digital and analog LSI's for communication use. He also worked in high-frequency analog IC's for satellite and optical communication systems. In 1989 he was transferred to the NTT Electronics Technology Corporation, Tokyo, Japan, where he is involved in the development of broadband GaAs analog IC's.

Mr. Kikuchi is a member of the Institute of Electronics, Information and Communication Engineers of Japan and the IEEE Microwave Theory and Techniques Society.

**Takashi Ono** was born in Tokyo, Japan, on April 15, 1964. He received the B.S. degree in electrical engineering from Waseda University, Tokyo, Japan, in 1987.

In 1987, he joined NTT Transmission Systems Laboratories, Yokosuka, Kanagawa, Japan, where he has been engaged in research on high-speed optical communication systems. His current research interests include high-speed semiconductor devices.

Mr. Ono is a member of the Institute of Electronics, Information, and Communications Engineers of Japan.